論理回路との整合性を検証 HLVS - Hierachical Layout versus Schematic

オプションモジュール

HLVSは、HLE(Hierarchical Layout ExtractorとLVS(Layout Versus Schematic)と言う二つのモジュールのことを指します。HLVSは物理的なレイアウトから電気的に接続しているデバイスを抽出し、物理設計の前段階である論理回路との整合性を検証するものです。もちろんdw-2000完全準拠のオプション製品ですから、GPEを用い様々なスクリプトと組み合わせてご使用頂くことにより、より効率的かつ迅速に作業を行うことが出来ます。

※XDRCモジュールをお買い求め頂くことにより、DLAの拡張機能をご使用頂けます。DLAの拡張機能についてはこちらをご参照下さい。

HLE

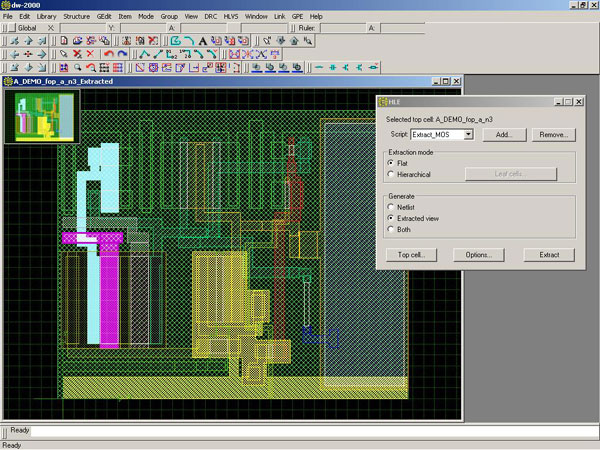

- HLEはエレクトリカルネットワーク、またはネットリストへ、物理的なレイアウトから電気的に接続しているデバイスを抽出するモジュールです。HLEはまずdw-2000レイアウトライブラリフォーマットの回路図からスタ-トします。そしてユーザー定義の関連情報を基にそのレイアウトの幾何学的関連からエレクトリカル部品を発見して行きます。これによりHLEはHSPICE形式のネットリストを作成して行きます。このネットリストへの抽出は複数階層にまたがって、もしくは単階層のみ、いずれでも可能です。

またHLEにはネットリストの一覧から抽出されたレイアウトを見渡すことが出来るネットワークナビゲーターも含まれています。これにより個々のアクティブエレメントに関する情報をクエリーしたり、個々のネットをハイライティング(反転)することができます。

さらにHLEにはより詳細な抽出情報を得られるよう、基本的な抽出操作に関するものからディスプレイ機能に渡るものまで、様々なGPEコマンドが装備されております。これにより例えば、誘導レイヤーへのコネクトや、MOSトランジスタ-のような基本デバイスの抽出も行うことが出来ます。他にも様々なデバイスやエレメントの作成・操作などを行えるアドバンストコマンドも備えており、より柔軟にタスクをこなして行ってくれます。

HLEモジュールは今日の設計の場で使用されている代表的な全てのデバイスの抽出をサポートしております。またサポートしていないデバイスでもユーザーにて定義していくことが可能です。また抽出に必要なスクリプトは抽出デバイス名と接続レイヤーを定義して行くだけなので、基本的な構築定義だけマスターすれば簡単に組んでいくことが出来ます。

LVS

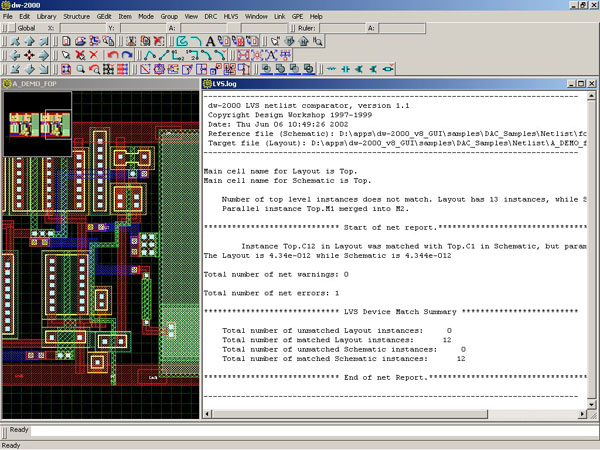

- LVSは、HLEを用いて物理レイアウトから抽出されたエレクトリカルネットワークを比較する為に使用されるネットワークコンパレーターです。つまり物理レイアウトエラーとミスマッチを検出するために使用されるコンパレ-タだと言うことです。LVSは検出された全ての不適合なソ-スの一覧表を作成します。これによりその二つのネットリスト間で許容できる差異を与えるための許容範囲の値を指定することが出来ます。また、非対称のセルだけを比較したりすることも出来ます。これにより二つのネットリスト上で同じオブジェクトを指しているにも関わらず、異なった名前とピンを持たせることが出来るようになります。

機能・特徴

GPEスクリプトを用いての抽出ルールの定義

先にも述べたように、HLVSはGPEに完全準拠しておりますので、GPEスクリプトを用いて抽出作業のルールを定義付けすることも簡単作業で行うことが出来ます。

複数階層・単階層抽出選択

複数階層にまたがって抽出するか、単階層にて抽出するか、はたまた複数階層の間にある一階層を抽出するか、を選択できる機能です。

寄生素子抽出

Basic C及びRC load寄生素子抽出を行います。

エレクトリカル視野表現及びナビゲーション

HLVSでは抽出された様子を視覚的に見ることが出来ます。これにより、より一層レイアウト上のエラー検出を簡単・確実に行うことが出来、同時に結線が確実に行われているかどうかのチェックも同時に行えるようになります。

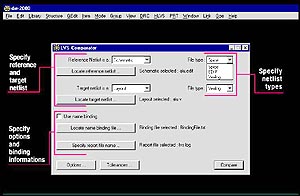

代表的なネットリスト形式のサポート

- HLVSでは以下の通りSPICE、Hspice、EDIF及びVerilogなどの代表的なネットリスト形式をサポートしております。これにより他ツールとの連携がスム-スに行えます。

セルマッピング機能

非対称セルのマッチングをすることができます。コンセプトは以下に記す通りです。通常Netlistは異なる集合フォーマットにてもたらされ、リマッピングメカニズムは完全なる翻訳精度を保証致します。

マッチング許容範囲

HLVSの比較コマンドは、パラレルトランジスタ-及び直列パラレル抵抗器のように同値マッピング操作をする能力を持っています。この柔軟性はスケマチック定義の自由度を大幅に向上いたします。

簡単GUI

HLVSはGUI(グラフィカルユーザーインターフェース)を採用することにより、レイアウトエディタ-のようにレイアウト上のエラーに即座に対処することが出来ます。

上記以外にも便利な機能・特長が豊富にあります。

こちらよりデモ版をダウンロードして、実際に体験いただけます。